#### **Features:**

- V<sub>DS</sub>, 30 V

- Maximum R<sub>DS(ON)</sub>, 1.3 mΩ

- I<sub>D</sub>, 60 A

- Pb-Free (RoHS Compliant), Halogen Free

### **Applications:**

- High Frequency DC-DC Conversion

- Motor Drive

- Industrial Automation

- Synchronous Rectification

- Inrush Protection

- Point-of-Load (POL) Converters

EPC2023 eGaN® FETs are supplied only in passivated die form with solder bars

Die Size: 6.05 mm x 2.3 mm

### **MAXIMUM RATINGS**

| Parameter                                                                         | Value                            |

|-----------------------------------------------------------------------------------|----------------------------------|

| V <sub>DS</sub> (Maximum Drain – Source Voltage)                                  | 30 V                             |

| V <sub>GS</sub> (Gate – Source Maximum Voltage Range)                             | -4 V < V <sub>GS</sub> < 6 V     |

| $I_D$ Continuous Drain Current, 25 °C, $\theta_{JA}$ = 13.5)                      | 60 A                             |

| I <sub>D</sub> (Maximum Pulsed Drain Current, 25 °C, T <sub>pulse</sub> = 300 μs) | 590 A                            |

| T <sub>J</sub> (Optimum Temperature Range)                                        | -40 °C < T <sub>J</sub> < 150 °C |

### **STATIC CHARACTERISTICS**

| Parameter                                                 | Conditions                                    | Value                                        |

|-----------------------------------------------------------|-----------------------------------------------|----------------------------------------------|

| I <sub>DSS</sub> (Maximum Drain – Source Leakage)         | $V_{DS} = 24 \text{ V}, V_{GS} = 0 \text{ V}$ | 1.0 mA                                       |

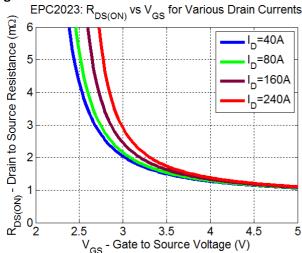

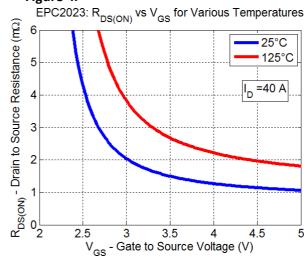

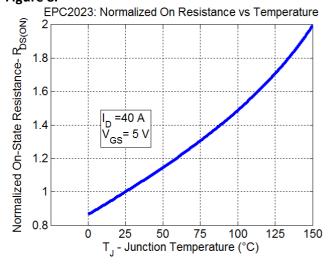

| R <sub>DS(ON)</sub> (Maximum R <sub>DS(ON)</sub> )        | $V_{GS} = 5 \text{ V}, I_D = 40 \text{ A}$    | 1.3 mΩ                                       |

| R <sub>DS(ON)</sub> (Typical R <sub>DS(ON)</sub> )        | $V_{GS} = 5 \text{ V}, I_D = 40 \text{ A}$    | 1 mΩ                                         |

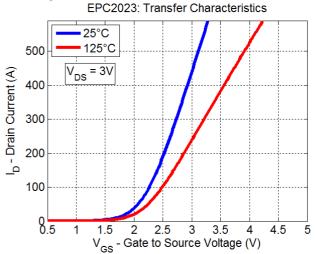

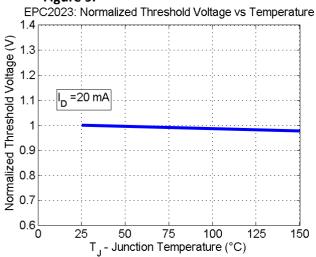

| V <sub>GS(TH)</sub> (Gate – Source Threshold Voltage)     | $V_{DS} = V_{GS}$ , $I_D = 20 \text{ mA}$     | $0.7 \text{ V} < V_{GS(TH)} < 2.5 \text{ V}$ |

| I <sub>GSS</sub> (Gate – Source Maximum Positive Leakage) | V <sub>GS</sub> = 5 V                         | 9 mA                                         |

| I <sub>GSS</sub> (Gate – Source Maximum Negative Leakage) | V <sub>GS</sub> = -4 V                        | -1 mA                                        |

www.epc-co.com

Specifications are with Substrate shorted to Source where applicable

T<sub>J</sub> = 25 °C unless otherwise stated

### **DYNAMIC CHARACTERISTICS**

| Parameter                                       | Conditions                                    | Typical Value |

|-------------------------------------------------|-----------------------------------------------|---------------|

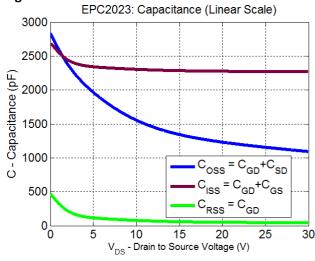

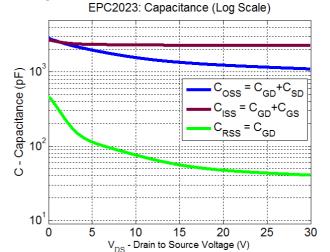

| C <sub>ISS</sub> (Input Capacitance)            | V <sub>DS</sub> = 15 V, V <sub>GS</sub> = 0 V | 2.3 nF        |

| C <sub>OSS</sub> (Output Capacitance)           |                                               | 1.3 nF        |

| C <sub>RSS</sub> (Reverse Transfer Capacitance) |                                               | 56 pF         |

| R <sub>G</sub> (Gate Resistance)                |                                               | 0.3 Ω         |

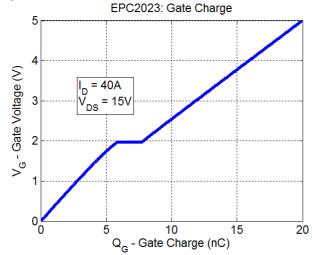

| Q <sub>G</sub> (Total Gate Charge)              | V <sub>DS</sub> = 15 V, I <sub>D</sub> = 40 A | 20 nC         |

| Q <sub>GS</sub> (Gate to Source Charge)         |                                               | 5.8 nC        |

| Q <sub>GD</sub> (Gate to Drain Charge)          |                                               | 1.9 nC        |

| Q <sub>G(TH)</sub> (Gate Charge at Threshold)   |                                               | 3.6 nC        |

| Q <sub>OSS</sub> (Output Charge)                | V <sub>DS</sub> = 15 V, V <sub>GS</sub> = 0 V | 28 nC         |

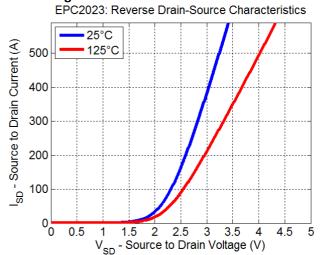

| Q <sub>RR</sub> (Source-Drain Recovery Charge)  |                                               | 0             |

$T_J = 25$  °C unless otherwise stated

### THERMAL CHARACTERISTICS

|                 |                                                  | TYP |      |

|-----------------|--------------------------------------------------|-----|------|

| $R_{\theta JC}$ | Thermal Resistance, Junction to Case             | 0.5 | °C/W |

| $R_{\theta JB}$ | Thermal Resistance, Junction to Board            | 1.4 | °C/W |

| $R_{\theta JA}$ | Thermal Resistance, Junction to Ambient (Note 1) | 42  | °C/W |

Note 1: R<sub>BJA</sub> is determined with the device mounted on one square inch of copper pad, single layer 2 oz copper on FR4 board.

Specifications are with Substrate shorted to Source where applicable

Figure 5a:

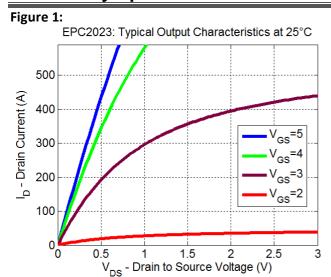

Figure 2:

Figure 4:

Figure 5b:

Figure 6:

Figure 8:

Figure 7:

Figure 9:

All measurements were done with substrate shorted to source

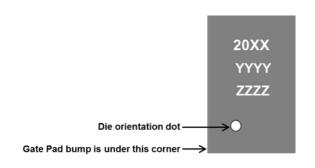

### **DIE MARKINGS**

|             | Laser Marking  |                |                |

|-------------|----------------|----------------|----------------|

| Part Number | Part # Marking | Lot_Date Code  | Lot_Date Code  |

|             | Line 1         | Marking Line 2 | Marking Line 3 |

| EPC2023ENGR | 20XX           | YYYY           | ZZZZ           |

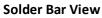

### **DIE OUTLINE**

| DIM | MICROMETERS |         |      |

|-----|-------------|---------|------|

|     | MIN         | Nominal | MAX  |

| А   | 6020        | 6050    | 6080 |

| В   | 2270        | 2300    | 2330 |

| С   | 2047        | 2050    | 2053 |

| d   | 717         | 720     | 723  |

| е   | 210         | 225     | 240  |

| f   | 195         | 200     | 205  |

| g   | 400         | 400     | 400  |

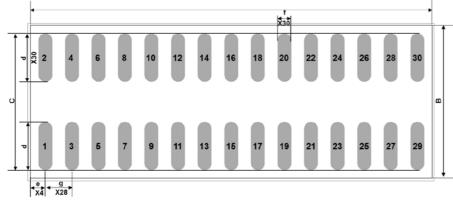

### **Side View**

www.epc-co.com

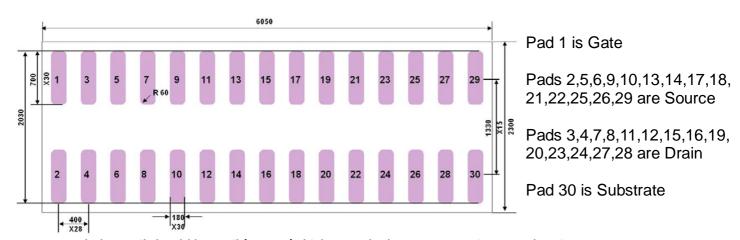

Pad 1 is Gate

Pads 2,5,6,9,10,13,14,17,18,21,22,25,26,29 are Source

Pads 3,4,7,8,11,12,15,16,19,20,23,24,27,28 are Drain

Pad 30 is Substrate

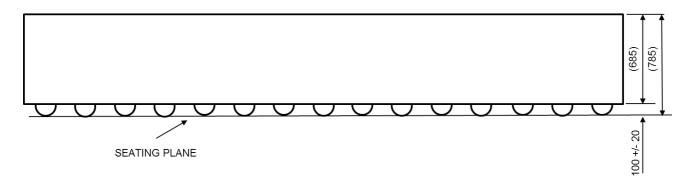

Land pattern is solder mask defined Solder mask opening is 10 µm smaller per side than bump

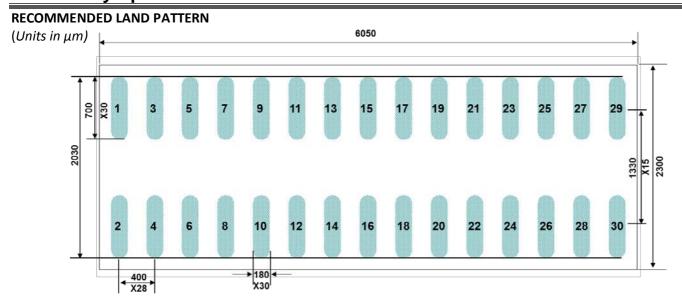

#### **RECOMMENDED STENCIL**

(Units in µm)

Recommended stencil should be 4mil (100 $\mu m$ ) thick, must be laser cut, openings per drawing.

Efficient Power Conversion Corporation (EPC) reserves the right to make changes without further notice to any products herein. Preliminary specification sheet contains information regarding a product EPC is considering for production release. EPC does not assume any liability arising out of the application or use of any product or circuit described herin; neither does it convey any license under its patent rights, nor the rights of other.

$eGaN^*$  is a registered trademark of Efficient Power Conversion Corporation. U.S. Patents 8,350,294; 8,404,508; 8,431,960; 8,436,398

Revised June, 2014